### I/O PROGRAMMING

### The x86 PC

assembly language, design, and interfacing fifth edition

MUHAMMAD ALI MAZIDI JANICE GILLISPIE MAZIDI DANNY CAUSEY

#### OBJECTIVES this chapter enables the student to:

- Code Assembly language instructions to read and write data to and from I/O ports.

- Diagram the design of peripheral I/O using the 74LS373 output latch and the 74LS244 input buffer.

- Describe the I/O address map of x86 PCs.

- List the differences in memory-mapped I/O versus peripheral I/O.

- Describe the purpose of a simple programmable peripheral interface chip.

#### 11.1: 8088 INPUT/OUTPUT INSTRUCTIONS

- All x86 processors, 8088 to Pentium<sup>®</sup>, can access external devices called *ports* using I/O instructions.

- Memory can contain both opcodes and data.

- I/O ports contain data only

- Two instructions: "OUT" and "IN" send data from the accumulator (AL or AX) to ports or bring data from ports into the accumulator.

### 11.1: 8088 INPUT/OUTPUT INSTRUCTIONS 8-bit data ports

- 8088 I/O operation is applicable to all x86 CPUs.

The 8-bit port uses the D0–D7 data bus for I/O devices.

- Register AL is used as the source/destination for IN/OUT instructions.

- To input or output data from any other registers, the data must first be moved to the AL register.

- Instructions OUT and IN have the following formats:

|         | Inputting Data |                   | Outputting Data |                   |  |

|---------|----------------|-------------------|-----------------|-------------------|--|

| Format: | IN             | dest, source      | OUT             | dest,source       |  |

| (1)     | IN             | AL,port#          | OUT             | port#,AL          |  |

| (2)     | MOV<br>IN      | DX,port#<br>AL,DX | MOV<br>OUT      | DX,port#<br>DX,AL |  |

© 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prentice Hall - Upper Saddle River, NJ 07458

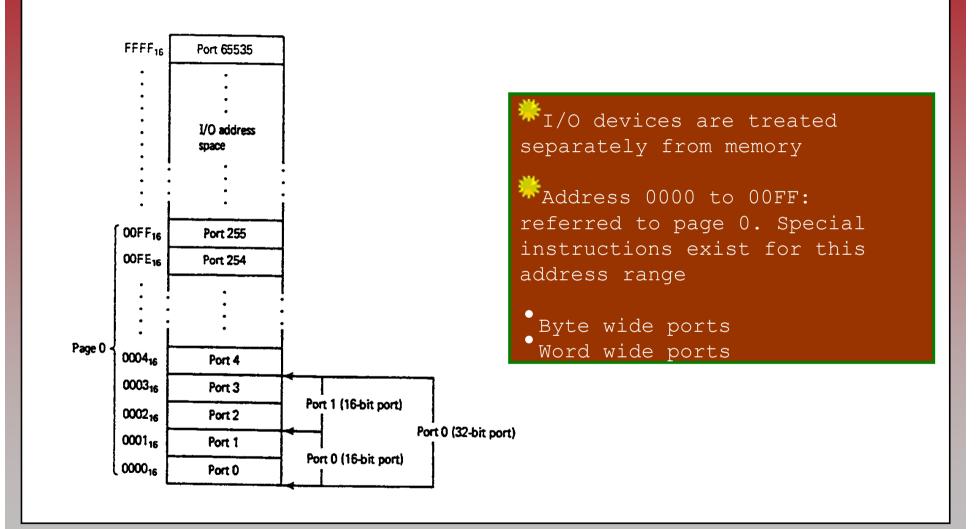

### Isolated I/O

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

© 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prentice Hall - Upper Saddle River, NJ 07458

#### Input Bus Cycle of the 8088

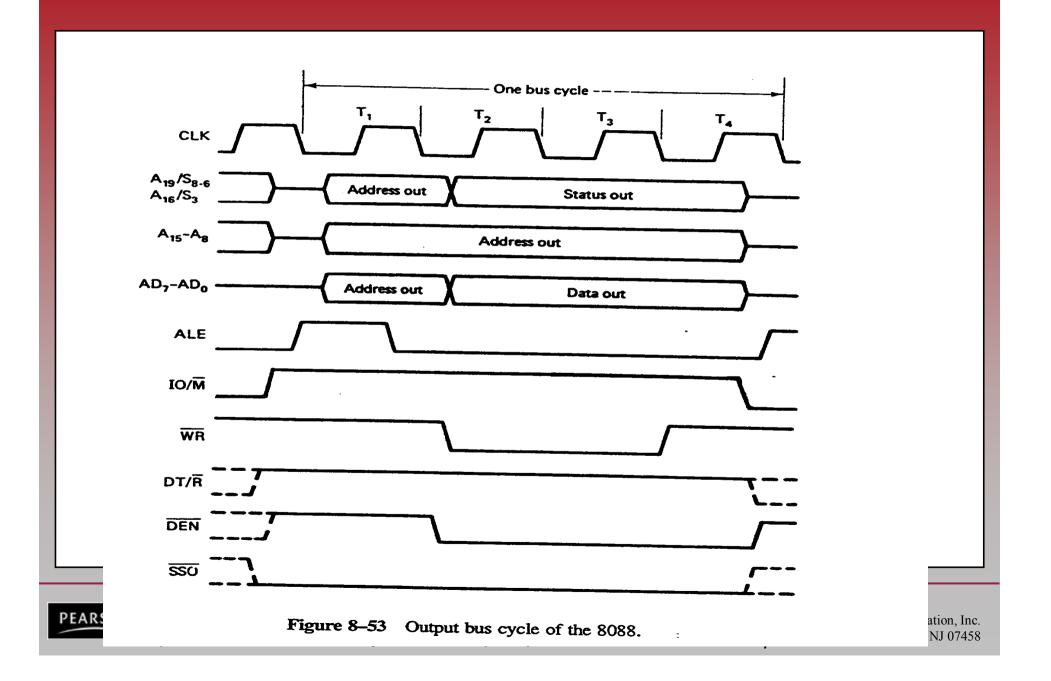

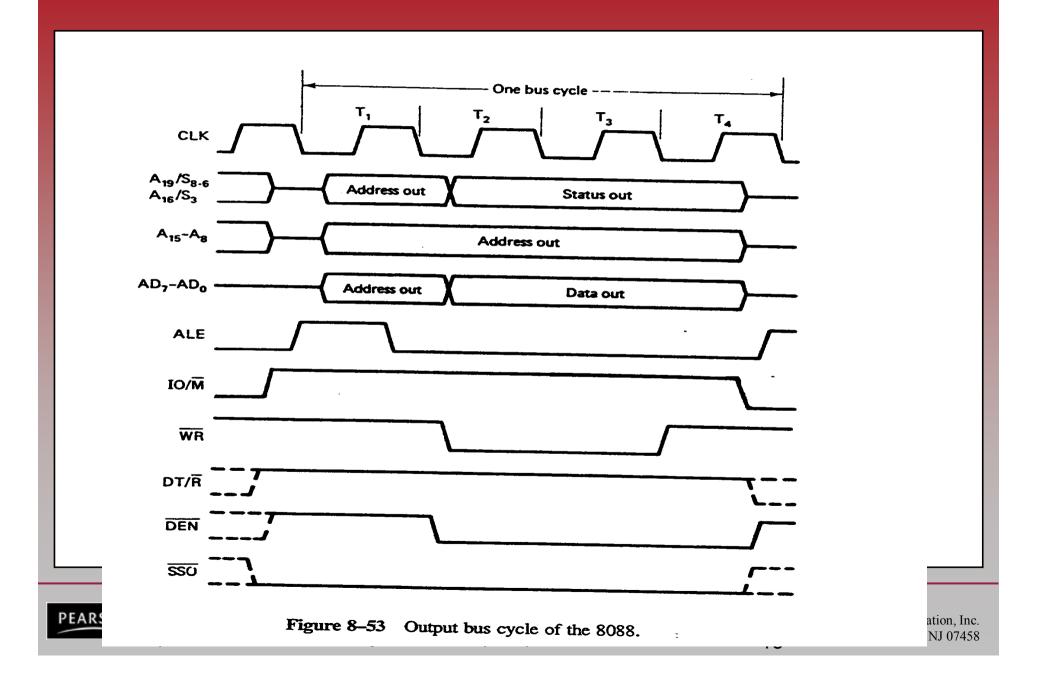

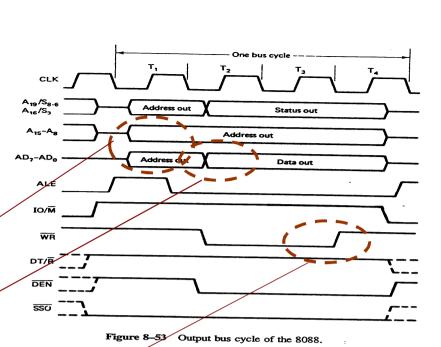

#### Output Bus Cycle of the 8088

## 11.1: 8088 INPUT/OUTPUT INSTRUCTIONS how to use I/O instructions

- I/O instructions are used in programming 8- and 16-bit peripheral devices.

- Printers, hard disks, and keyboards.

- For an 8-bit port, use *immediate addressing*:

| MOV | AL,36H | ;AL=36 | 5H    |     |    |      |         |     |

|-----|--------|--------|-------|-----|----|------|---------|-----|

| OUT | 43H,AL | ;send  | value | 36H | to | port | address | 43H |

## 11.1: 8088 INPUT/OUTPUT INSTRUCTIONS how to use I/O instructions

- 16-bit port address instruction using *register indirect* addressing mode with register DX.

- This program toggles port address 300H continuously.

| BACK: | MOV | DX,300H  | ;DX = port address 300H |

|-------|-----|----------|-------------------------|

|       | MOV | AL,55H   |                         |

|       | OUT | DX,AL    | ;toggle the bits        |

|       | MOV | AL, OAAH |                         |

|       | OUT | DX,AL    | ;toggle the bits        |

|       | JMP | BACK     |                         |

Only **DX** can be used for 16-bit I/O addresses.

Use register AL for 8-bit data.

### I/O Instructions

Example. Write a sequence of instructions that will output the data FFh to a byte wide output at address ABh of the I/O address space MOV AL,0FFh OUT 0ABh, AL

**Example**. Data is to be read from two byte wide input ports at addresses AAh and A9h and then this data will then be output to a word wide output port at address B000h

IN AL, 0AAh MOV AH,AL IN AL, 0A9h MOV DX,0B00h OUT DX,AX

### 11.1: 8088 INPUT/OUTPUT INSTRUCTIONS how to use I/O instructions

# Example shows decision making based on the data that was input.

#### Example 11-1

In a given 8088-based system, port address 22H is an input port for monitoring the temperature. Write Assembly language instructions to monitor that port continuously for the temperature of 100 degrees. If it reaches 100, then BH should contain 'Y'.

#### Solution:

| BACK: | IN  | AL,22H | ;get the temperature from port # 22H |

|-------|-----|--------|--------------------------------------|

|       | CMP | AL,100 | ;is temp = 100?                      |

|       | JNZ | BACK   | ; if not, keep monitoring            |

|       | MOV | ΒН, 'Υ | ;temp = 100, load 'Y' into BH        |

#### Input Bus Cycle of the 8088

#### Output Bus Cycle of the 8088

### I/O Example

- Assume that AX = 76A9h.: Analyze the data transfer for a) 8088 b) 8086 when MOV DX, 648h OUT DX,AX

- 8088 case

- 1<sup>st</sup> bus cycle

- T1: Address 0648h is put on pins AD0-AD7, A8-15 and latched when ALE is activated

- T2: The low byte A9h is put on the data bus pins AD0-AD7 and IOWC is activated

- T3: Setup time

- T4: Byte is written to the port assuming zero wait states

- 2<sup>nd</sup> Bus Cycle (Similar to 1<sup>st</sup> Bus Cycle)

- T1: Address 0649h is put on pins AD0-AD7, A8-15 and latched when ALE is

The x86 PC **activated** Assembly Language, Besign, and Interfacing By Muhammud Ali Mazid, Gandel Gepi Oytican 76h, is sput on the datars buse plans part of the River, NJ 07458

#### Example continued

- 8086 case

- T1: Address 0648h is put on pins AD0-AD15 plus BHE=low is latched by the 74LS373 when ALE is activated

- T2: 76A9h, the contents of AX, is put on ADC

TA9h the top of the properties of the port of the port

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

© 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prentice Hall - Upper Saddle River, NJ 07458

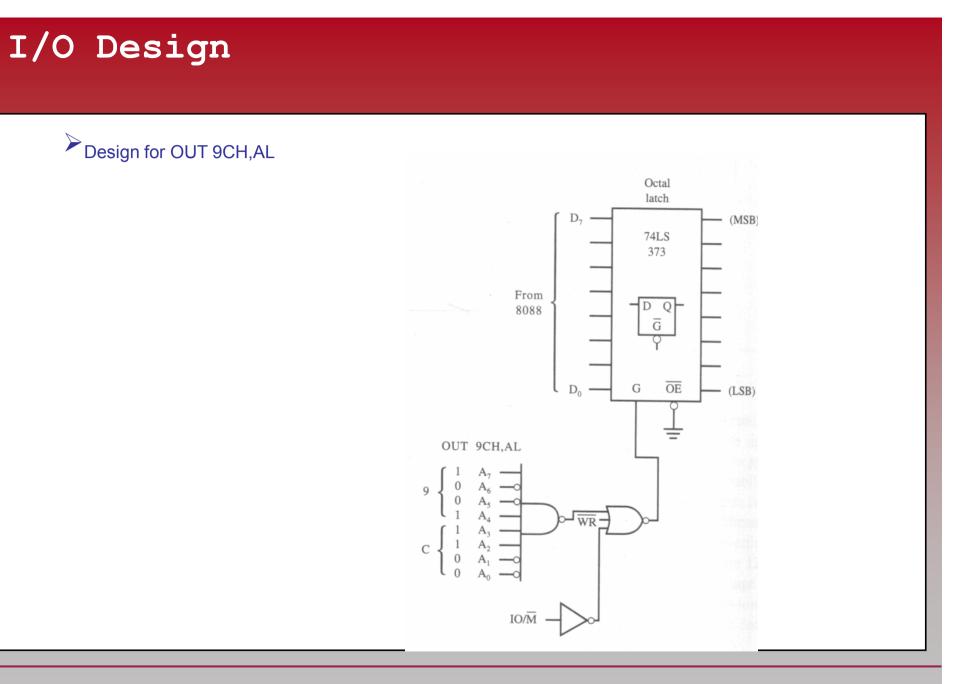

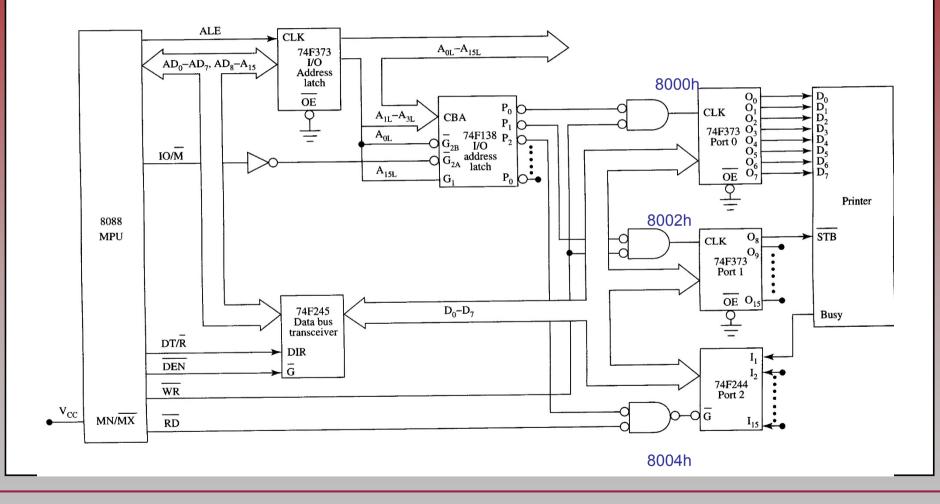

### I/O Design in the 8088/86

- In every computer, when data is sent out by the CPU, the data on the data bus must be latched by the receiving device

- While memories have an internal latch to grab the data on the data bus, a latching system must be designed for ports

- Since the data provided by the CPU to the port is on the system data bus for a limited amount of time (50 -1000ns) it must be <u>latched</u> before it is lost

- Likewise, when data is coming in by way of a data bus (either from port or memory) it must come in through a <u>three-state buffer</u>

**PEARSON** *The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

© 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prentice Hall - Upper Saddle River, NJ 07458

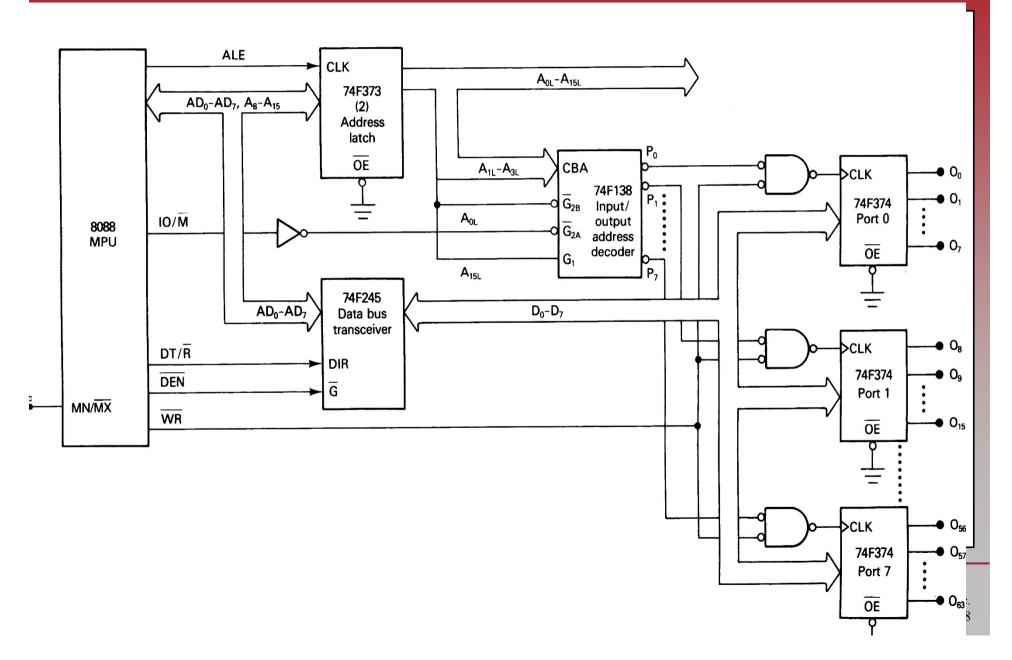

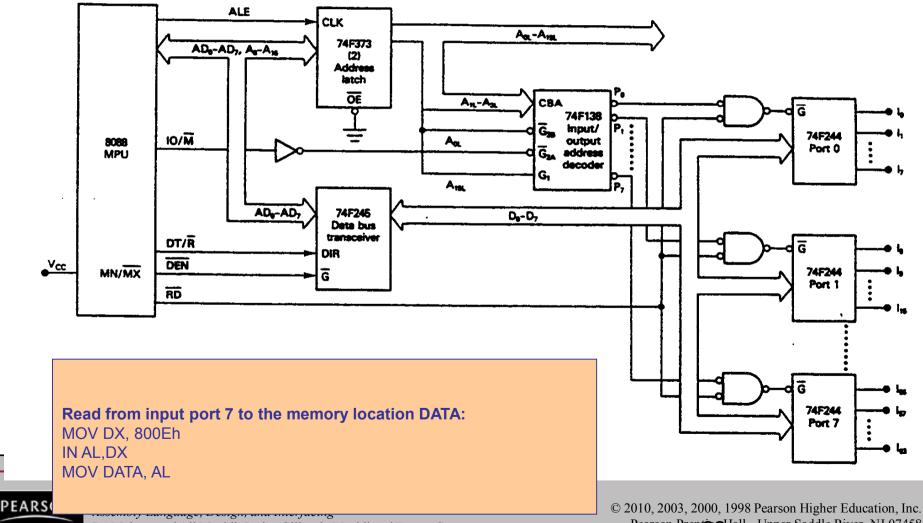

### Example - 64 line parallel output circuit - 8088

#### Examples

- To which output port in the previous figure are data written when the address put on the bus during an output bus cycle is 8002h?

- A15 .. A0 = 1000 0000 0000 0010b

- A15L = 1

- -A0L = 0

- $\overline{A3LA2LA1L} = 0.01$ Write a sequence of instructions that output the byte contents of the memory address DATA to output port pin the previous figure

MOV DX, 8000h MOV AL,DATA OUT DX, AL

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

© 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prentic Hall - Upper Saddle River, NJ 07458

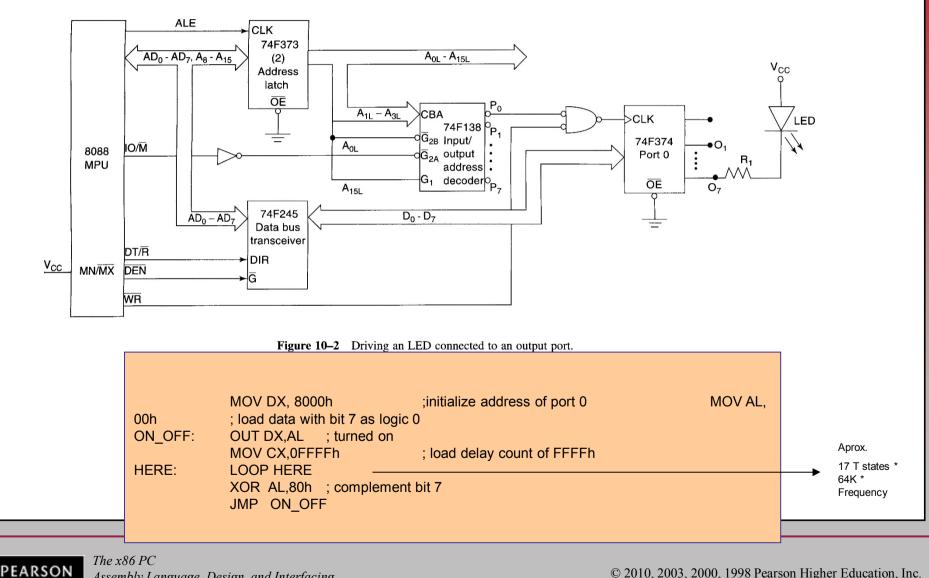

### Time Delay Loop and Blinking a LED at an Output

Assembly Language, Design, and Interfacing By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey © 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prenting Hall - Upper Saddle River, NJ 07458

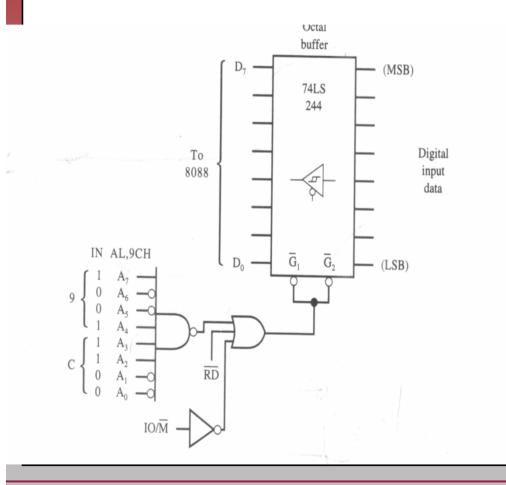

#### IN port design using the 74LS244

Design for IN AL,9CH

In order to prevent any unwanted data (garbage) to come into the system (global) data bus, all input devices must be isolated through the tri-state buffer. The 74LS244 not only plays this role but also provides the incoming signals sufficient strength (driving capability) to travel all the way to the CPU

It must be emphasized that every device (memory, peripheral) connected to the global data bus must have a latch or a tri-state buffer. In some devices such as memory, they are internal but must be present.

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

© 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prenting Hall - Upper Saddle River, NJ 07458

#### Example - 64 line parallel input circuit

By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

Pearson Prentige Hall - Upper Saddle River, NJ 07458

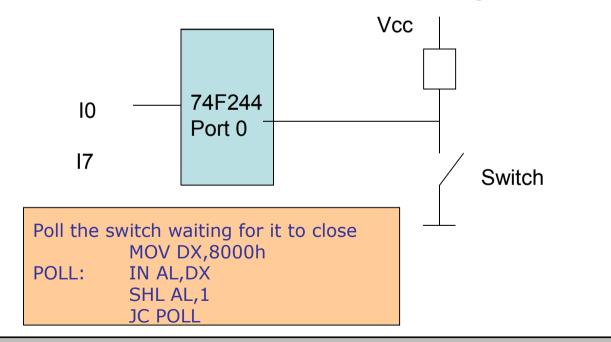

#### Interrupts vs Polling

CPU services devices in two ways:

Interrupts and Polling

- In the interrupt method, whenever the device needs the service of the CPU, the device informs the CPU by sending an interrupt signal.

- The CPU interrupts whatever it is doing and serves the request

- The advantage of interrupts is that the CPU can serve many devices

- Each receives a service based on its priority

- Disadvantage of interrupts is that they require more hardware and software

- In polling, CPU monitors continuously a status condition and when the conditions are met, it will perform the service.

- In contrast, polling is cheap and requires minimal software

- But it ties down the CPU

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

© 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prentice Hall - Upper Saddle River, NJ 07458

#### Example

In practical applications, it is sometimes necessary within an I/O service routine to repeatedly read the value at an input line and test this value for a specific logic level.

© 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prenting Hall - Upper Saddle River, NJ 07458

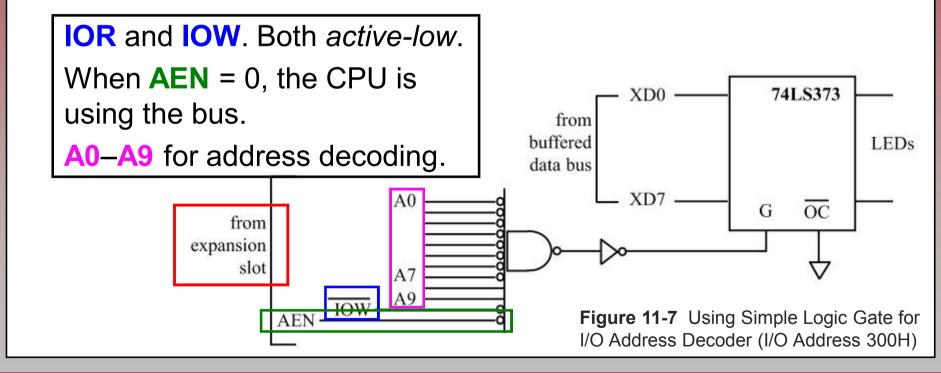

#### 11.2: I/O ADDRESS DECODING AND DESIGN

- The concept of address bus decoding for I/O instructions is exactly the same as for memory.

- 1. The control signals IOR and IOW are used along with the decoder.

- 2. For an 8-bit port address, **A0**-**A7** is decoded.

- 3. If the port address is 16-bit (using DX), A0–A15 is decoded.

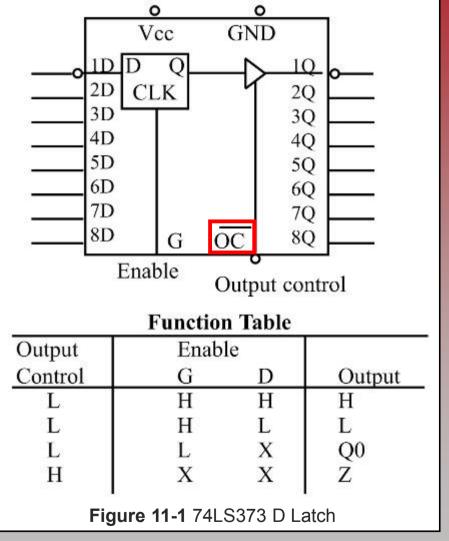

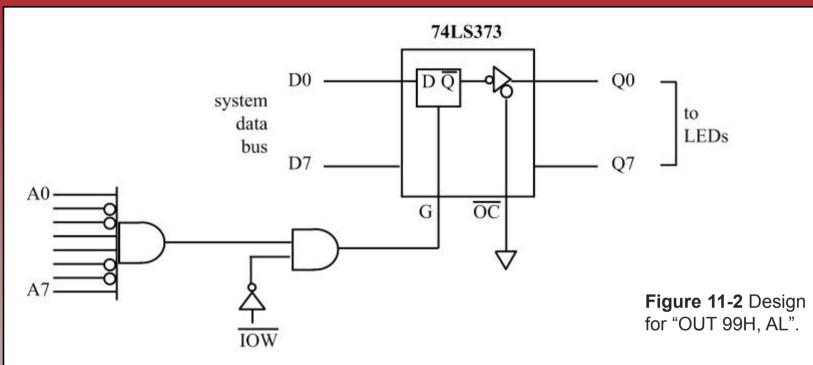

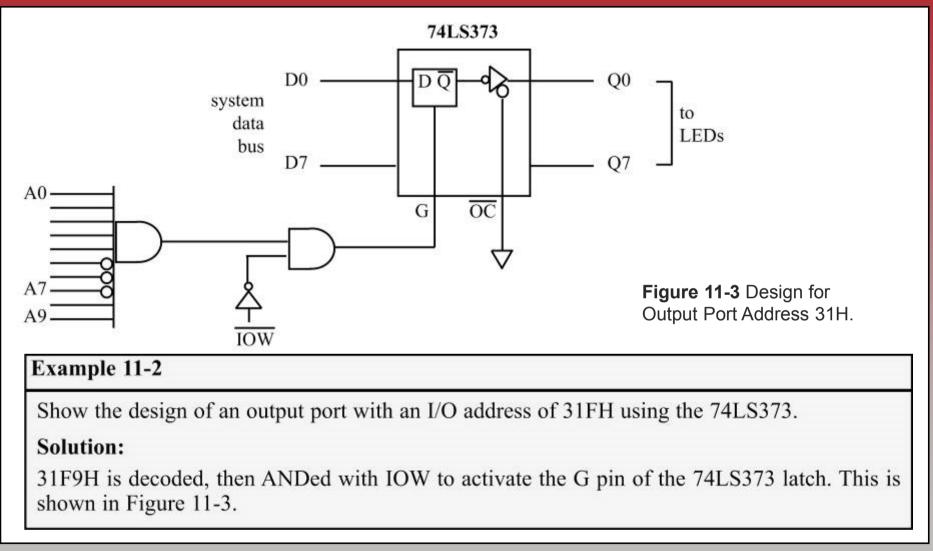

## 11.2: I/O ADDRESS DECODING AND DESIGN using 74LS373 in an output port design

74LS373 can be used as a latching system for simple I/O ports.

– Pin **OC** must be grounded.

## 11.2: I/O ADDRESS DECODING AND DESIGN using 74LS373 in an output port design

• For an output latch, it is common to AND the output of the address decoder with control signal **IOW**.

- To provide the latching action.

## 11.2: I/O ADDRESS DECODING AND DESIGN using 74LS373 in an output port design

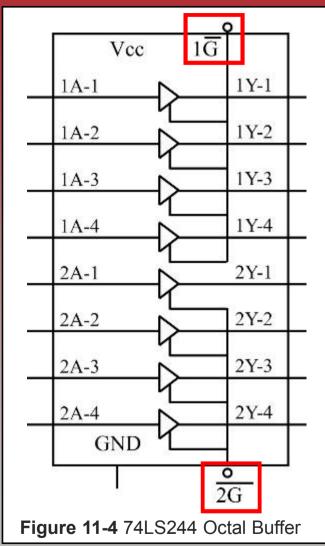

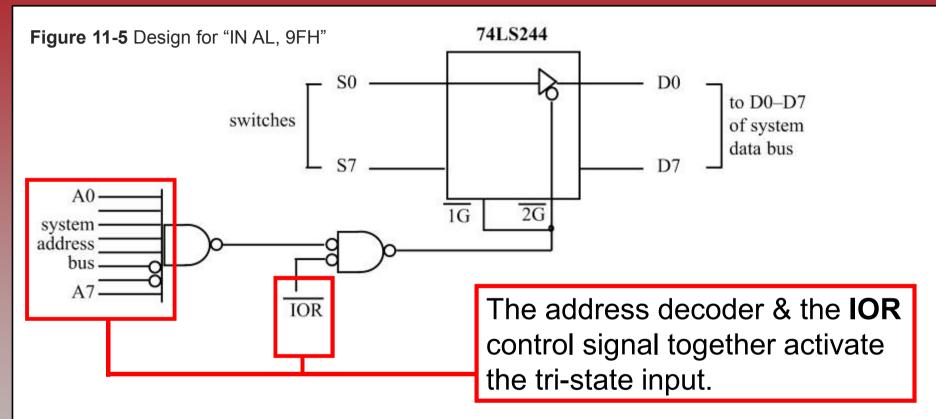

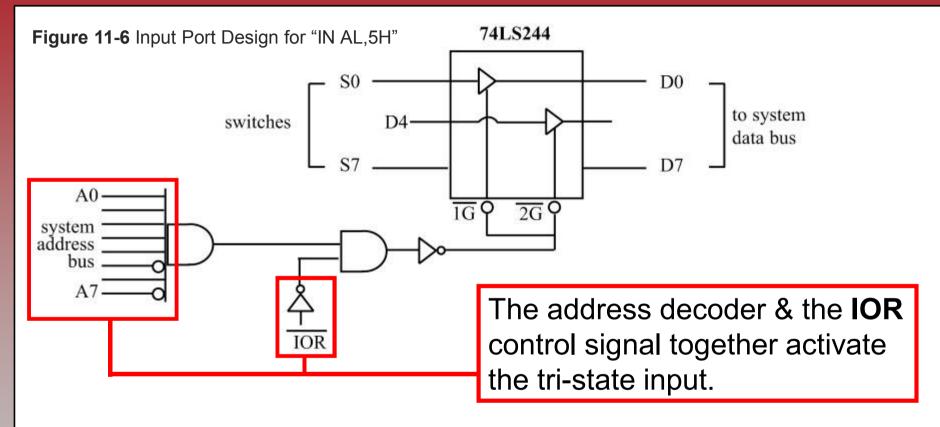

#### 11.2: I/O ADDRESS DECODING AND DESIGN IN port design using 74LS244

- Data from a data bus, must come in through a three-state buffer—referred to as *tristated*.

- Simple input ports we use the 74LS244 chip.

- Since **1G & 2G** each control only 4 bits of 74LS244, they *both* must be activated for 8-bit input.

### 11.2: I/O ADDRESS DECODING AND DESIGN IN port design using 74LS244

74LS244 is widely used for buffering and providing high driving capability for unidirectional buses.

### 11.2: I/O ADDRESS DECODING AND DESIGN IN port design using 74LS244

74LS244 as an entry port to the system data bus.

- Used for bidirectional buses, as seen in Chapter 9.

# 11.2: I/O ADDRESS DECODING AND DESIGN memory-mapped I/O

- Communicating with I/O devices using IN and OUT instructions is referred to as *peripheral I/O*.

- Some designers also refer to it as *isolated I/O*.

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

© 2010, 2003, 2000, 1998 Pearson Higher Education, Inc. Pearson Prentice Hall - Upper Saddle River, NJ 07458

# 11.2: I/O ADDRESS DECODING AND DESIGN memory-mapped I/O

- Some processors do not have IN & OUT instructions, but use *Memory-mapped I/O*.

- A memory location is assigned as an input or output port.

- Instructions access memory locations to access I/O ports.

- Instead of IN and OUT instructions.

- The entire 20-bit address, A0-A19, must be decoded.

- The **DS** register must be loaded prior to accessing memory-mapped I/O.

- In memory-mapped I/O interfacing, control signals

MEMR and MEMW are used.

- Memory I/O ports can number as high as 2<sup>20</sup> (1,048,576).

## 11.2: I/O ADDRESS DECODING AND DESIGN memory-mapped I/O

- Some processors do not have IN & OUT instructions, but use *Memory-mapped I/O*.

- Memory-mapped I/O can perform arithmetic & logic operations on I/O data directly without first moving them into the accumulator.

- Memory-mapped I/O uses memory address space, which could lead to memory space fragmentation.

#### Example 11-3

Show the design of "IN AL,9FH" using the 74LS244 as a tri-state buffer.

#### Solution:

9FH is decoded, then ANDed with IOR. To activate OC of the 74LS244, it must be inverted since OC is an active-low pin. This is shown in Figure 11-5.

#### 11.3: I/O ADDRESS MAP OF x86 PCs

| <u>Hex Range</u><br>000–01F<br>020–03F                                             | Device<br>DMA controller 1, 8237A-5<br>Interrupt controller 1, 8259A, Master                                                                                           | <u>Hex Range</u><br>378–37F<br>380–38F          | <u>Device</u><br>Parallel printer port 1<br>SDLC, bisynchronous 2                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to make ful<br>compatible<br>the I/O ma<br>The addres                              | of the original IBM PC<br>II use of I/O instruction<br>with the x86 IBM PC<br>p of Table 11-1, shown<br>as range <b>300–31FH</b> is<br>be cards to be plugged<br>slot. | ns. To be<br>, follow<br>n here.<br>s set aside | Cluster<br>Bisynchronous 1<br>Monochrome display/printer adapter<br>Enhanced graphics adapter<br>Color graphics monitor adapter<br>Disk controller<br>Serial port 1<br>Data acquisition (adapter 1)<br>Cluster (adapter 1)<br>Data acquisition (adapter 2)<br>Cluster (adapter 2)<br>Data acquisition (adapter 3)<br>Cluster (adapter 3)<br>GPIB (adapter 1)<br>Cluster (adapter 4) |

| 2E1<br>2E2 & 2E3<br>2F8-2FF<br>300-31F<br>360-363<br>364-367<br>368-36B<br>36C-36F | GPIB (adapter 0)<br>Data acquisition (adapter 0)<br>Serial port 2<br>Prototype card<br>PC network (low address)<br>Reserved<br>PC network (high address)<br>Reserved   | 42E1<br>62E1<br>82E1<br>A2E1<br>C2E1<br>E2E1    | GPIB (adapter 2)<br>GPIB (adapter 3)<br>GPIB (adapter 4)<br>GPIB (adapter 5)<br>GPIB (adapter 6)<br>GPIB (adapter 7)                                                                                                                                                                                                                                                                |

#### See the entire I/O map on page 296 of your textbook.

#### 11.3: I/O ADDRESS MAP OF x86 PCs absolute vs. linear address decoding

- In decoding addresses, either all or a selected number of them are decoded.

- In absolute decoding, all address lines are decoded.

- If only selected address pins are decoded, it is called *linear select* decoding.

- Linear select is cheaper, but creates aliases, the same port with multiple addresses.

- If you see a large gap in the I/O address map of the x86

PC, it is due to the address aliases of the original PC.

# 11.3: I/O ADDRESS MAP OF x86 PCs prototype addresses 300-31FH in x86 PC

- Prototype cards at **300H–31FH** can be data acquisition boards used to monitor analog signals.

- Temperature, pressure, etc., inputs use signals on the 62-pin section of the ISA expansion slot.

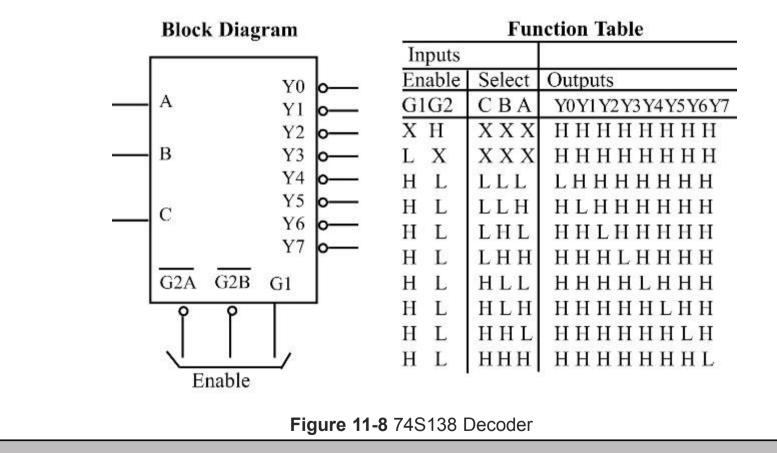

# 11.3: I/O ADDRESS MAP OF x86 PCs 74LS138 as a decoder

• NANDs, inverters, and 74LS138 chips for decoders can be applied to I/O address decoding.

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

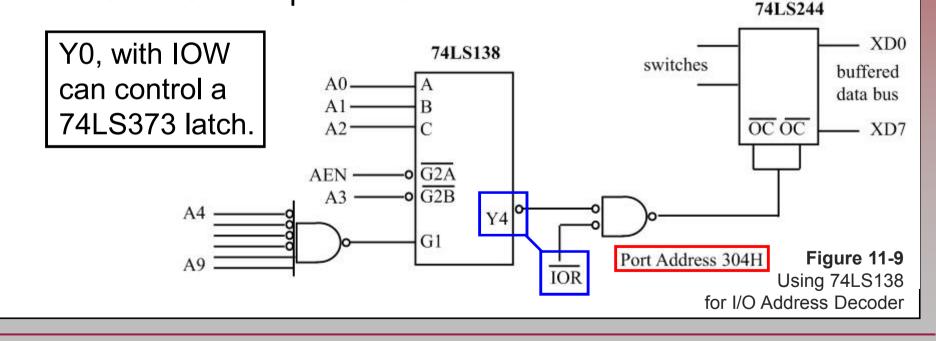

## 11.3: I/O ADDRESS MAP OF x86 PCs 74LS138 as a decoder

- 74LS138 showing I/O address decoding for an input port located at address **304H**.

- Each Y output controls a single I/O device.

- Y4 output, together with the signal at IOR, controls the 74LS244 input buffer.

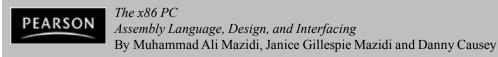

## 11.3: I/O ADDRESS MAP OF x86 PCs 74LS138 as IBM PC I/O address decoder

- A0 to A4 go to individual peripheral input addresses.

- A5, A6, & A7 handle output selection of outputs Y0 to Y7.

- Pins A8, A9, & AEN all must be *low* to enable 74LS138.

- AEN is low only when the x86 is in control of the system bus.

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

# 11.3: I/O ADDRESS MAP OF x86 PCs port 61H and time delay generation

• Port 61H, a widely used port, can be used to generate a time delay.

– In any PC from the 286 to the Pentium<sup>®</sup>.

- I/O port 61H has eight bits (D0–D7), of which D4 is of particular interest.

- In all 286 & higher PCs, D4 of port 61H changes its state, indefinitely every 15.085 microseconds (ms).

- Low for 15.085 ms.

- High for the same amount of time.

- Low again.

# 11.3: I/O ADDRESS MAP OF x86 PCs port 61H and time delay generation

• The following program uses port 61H to generate a 1/2 second delay in all bits of port 310H.

; TOGGLING ALL BITS OF PORT 310H EVERY 0.5 SEC MOV DX,310H HERE: MOV AL, 55H ;toggle all bits OUT DX, AL MOV CX,33144; delay=33144x15.085 us=0.5 sec CALL TDELAY MOV AL, OAAH OUT DX, AL MOV CX,33144 See the entire CALL TDELAY program listing HERE TMP on page 299 of your textbook. (MORE)

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

# 11.3: I/O ADDRESS MAP OF x86 PCs port 61H and time delay generation

- When 61H is read, all bits are masked except D4.

- The program waits for D4 to change, before it loops again.

| ;CX=COUNT |      |         | 510                   |

|-----------|------|---------|-----------------------|

| TDELAY    | PROC | NEAR    |                       |

|           | PUSH | AX      | ;save AX              |

| W1:       | IN   | AL,61H  |                       |

|           | AND  | AL,0001 | 0000B                 |

|           | CMP  | AL,AH   |                       |

|           | JE   | W1      | ;wait for 15.085 usec |

|           | MOV  | AH,AL   |                       |

|           | LOOP | Wl      | ;another 15.085 usec  |

|           | POP  | AX      | ;restore AX           |

|           | RET  |         |                       |

| TDELAY    | ENDP |         |                       |

See the entire program listing on page 299 of your textbook.

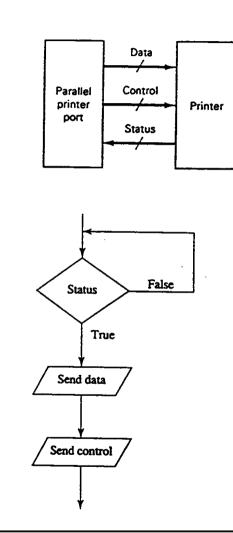

#### Parallel Printer Interface

| Pin | Assignment  |

|-----|-------------|

| 1   | Strobe      |

| 2   | Data 0      |

| 3   | Data 1      |

| 4   | Data 2      |

| 5   | Data 3      |

| 6   | Data 4      |

| 7   | Data 5      |

| 8   | Data 6      |

| 9   | Data 7      |

| 10  | Ack         |

| 11  | Busy        |

| 12  | Paper Empty |

| 13  | Select      |

| 14  | Auto Foxt   |

| 15  | Error       |

| 16  | Initialize  |

| 17  | Sictin      |

| 18  | Ground      |

| 19  | Ground      |

| 20  | Ground      |

| 21  | Ground      |

| 22  | Ground      |

| 23  | Ground      |

| 24  | Ground      |

| 25  | Ground      |

|     |             |

| Data:         | Data0, Data1,, Data7                          |

|---------------|-----------------------------------------------|

| Control:      | Strobe<br>Auto Foxt<br>Initialize<br>Slctin   |

| Status:       | Ack<br>Busy<br>Paper Empty<br>Select<br>Error |

| ACK is used b | by printer to acknowledge receipt of data and |

can accept a new character.

BUSY high if printer is not ready to accept a new character

SELECT when printer is turned on

ERROR goes low when there are conditions such as paper jam, out of paper, offline

STROBE when PC presents a character

**INITIALIZE** Clear Printer Buffer and reset control

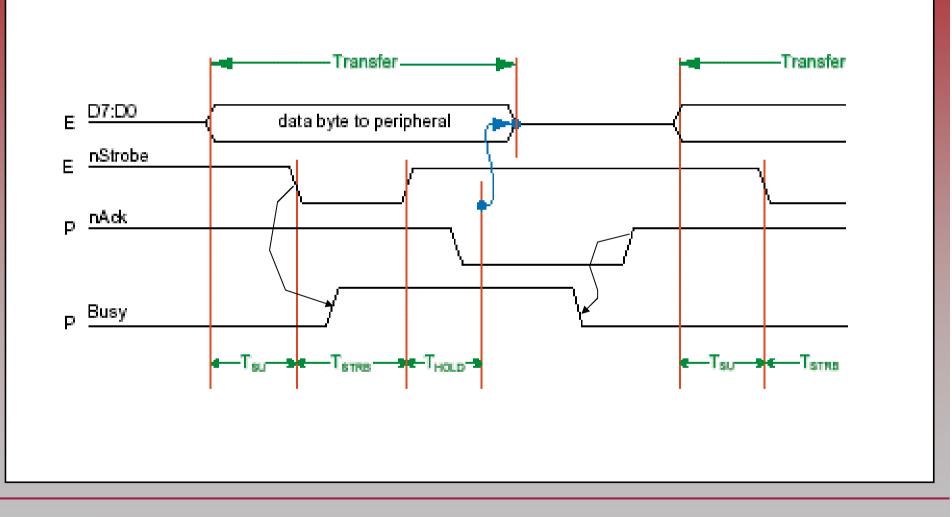

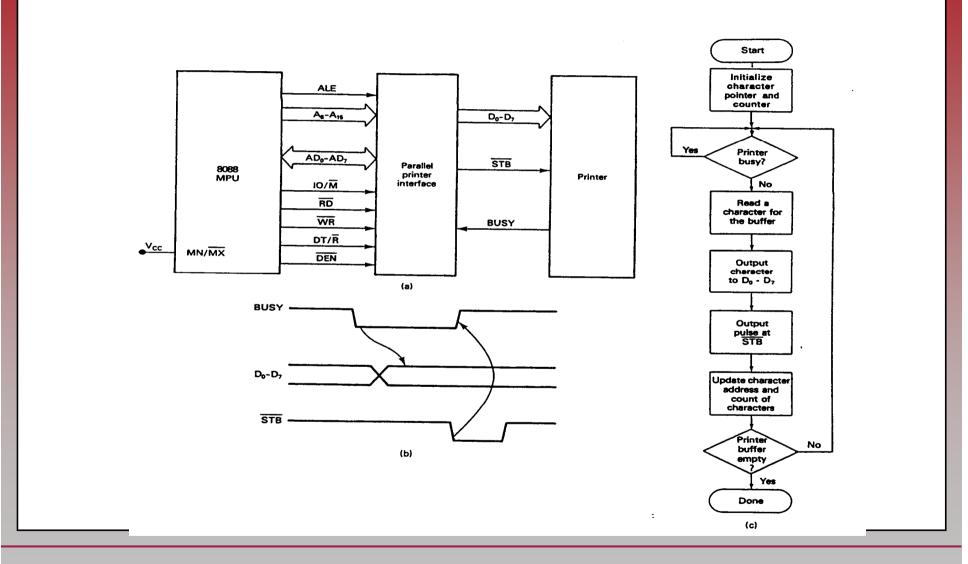

#### Operational Principle - Parallel Printer Port

- The computer checks the BUSY signal from the printer, if not BUSY then

- When the PC presents a character to the data pins of the printer, it activates the STROBE pin, telling it that there is a byte sitting at the data pins. Prior to asserting STROBE pin, the data must be at at the printer's data pins for at least 0.5 microsec. (data setup time)

- The STROBE must stay for 0.5

microsec

- The printer asserts BUSY pin indicating the computer to wait

- When the printer picks up the data, it sends back the ACK signal, keeps

ACK low for 5 microsec.

- As the ACK signal is going high, the printer makes the BUSY pin low to indicate that it is ready to accept the next byte

- The CPU can use ACK or BUSY signals from the printer to initiate the process of sending another byte

#### Handshaking

#### Printer Interface Circuit

|   |           | that implements the flowchart. Character data is held in memory starting at address PRNT_BUFF,<br>aracters held in the buffer is identified by the count address CHAR_COUNT.<br>MOV CL, CHAR_COUNT<br>MOV SI, OFFSET PRNT_BUFF |             |                     |  |  |  |

|---|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|--|--|--|

| Ρ | OLL_BUSY: | MOV DX,8004h<br>IN AL,DX<br>AND AL,01h<br>JNZ POLL_BUSY                                                                                                                                                                        |             | BUSY input checked  |  |  |  |

|   |           | MOV AL, [SI]<br>MOV DX,8000h<br>OUT DX,AL                                                                                                                                                                                      |             | Character is output |  |  |  |

|   |           | MOV AL, 00h<br>MOV DX,8002h<br>OUT DX,AL                                                                                                                                                                                       | ;STB = 0    | So as the strobe    |  |  |  |

|   |           | MOV BX,0Fh<br>STROBE: DEC BX<br>JNZ STROBE<br>MOV AL,01h                                                                                                                                                                       | ; delay for | STB = 0             |  |  |  |

|   |           | OUT DX,AL<br>INC SI<br>DEC CL<br>JNZ POLL_BUSY                                                                                                                                                                                 | ; STB bar = | = 1                 |  |  |  |

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

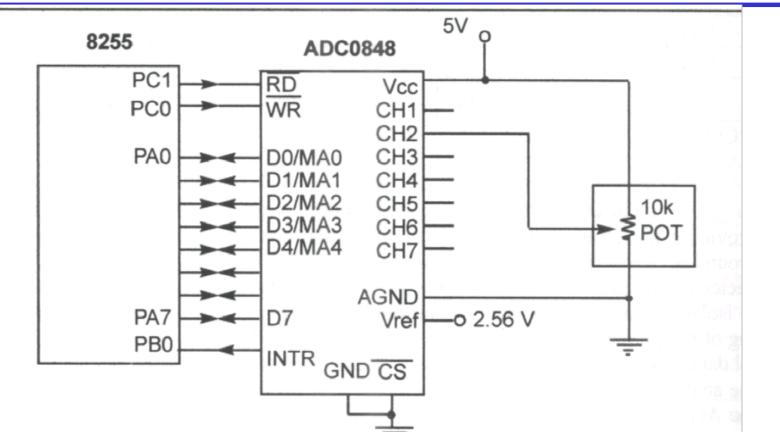

#### 11.4: PROGRAMMING & INTERFACING THE 8255

- The 8255 is a widely used 40-pin, DIP I/O chip.

- It has three separately accessible programmed ports, A, B & C.

- Each port can be programmed to be input or output.

- Ports can also be changed dynamically.

| Port A (PA0–PA7)<br>Port B (PB0–PB7)<br>Port C (PC0–PC7) | These 8-bit<br>ports can<br>be all input<br><i>or</i> all output |

|----------------------------------------------------------|------------------------------------------------------------------|

| · · · · · · · · · · · · · · · · · · ·                    |                                                                  |

| <u>г</u> |        | 7 |       | -  | 1 |

|----------|--------|---|-------|----|---|

|          | 1 PA3  |   | / PA4 | 40 |   |

|          | 2 PA2  |   | PA5   | 39 |   |

|          | 3 PA1  |   | PA6   | 38 |   |

|          | 4 PA0  |   | PA7   | 37 |   |

|          | 5 RD   |   | WR    | 36 |   |

|          | 6 CS   |   | RESET | 35 |   |

|          | 7 GND  | 8 | D0    | 34 |   |

|          | 8 A1   |   | D1    | 33 |   |

|          | 9 A0   | 2 | D2    | 32 |   |

|          | 10 PC7 | 5 | D3    | 31 |   |

|          | 11 PC6 |   | D4    | 30 |   |

|          | 12 PC5 | 5 | D5    | 29 |   |

|          | 13 PC4 | Α | D6    | 28 |   |

|          | 14 PC0 |   | D7    | 27 |   |

|          | 15 PC1 |   | Vcc   | 26 |   |

|          | 16 PC2 |   | PB7   | 25 |   |

|          | 17 PC3 |   | PB6   | 24 |   |

|          | 18 PB0 |   | PB5   | 23 |   |

|          | 19 PB1 |   | PB4   | 22 |   |

|          | 20 PB2 |   | PB3   | 21 |   |

| J.       |        |   |       | -  | 1 |

Figure 11-11 8255 PPI Chip

#### 11.4: PROGRAMMING & INTERFACING THE 8255

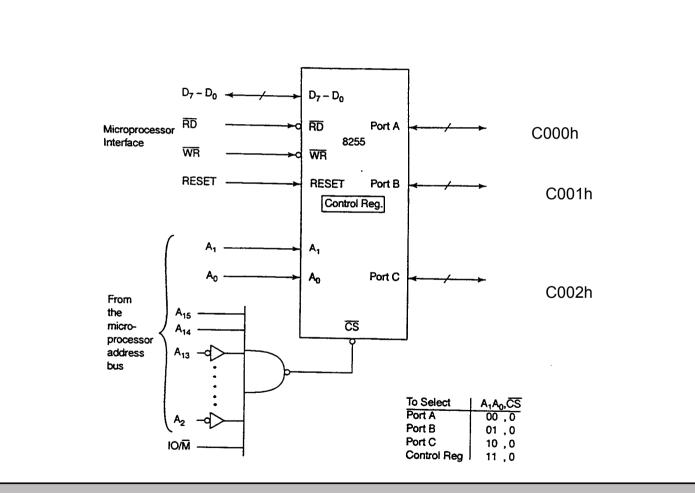

- RD and WR active-low 8255 control signal inputs.

- If the 8255 is using peripheral I/O, IOR & IOW of the system bus are connected to these two pins.

- If memory-mapped I/O, MEMR & MEMW activate them.

- **RESET** an active-high signal input into the 8255, used to clear the control register.

- All ports are initialized as input ports.

#### 11.4: PROGRAMMING & INTERFACING THE 8255

- A0, A1, and CS

- **CS** (chip select) selects the entire chip.

- Address pins A0 and A1 select the specific port within the 8255.

These three pins are used to access ports A, B, C, or the control register.

| CS | A1 | A0 | Selects              |

|----|----|----|----------------------|

| 0  | 0  | 0  | Port A               |

| 0  | 0  | 1  | Port B               |

| 0  | 1  | 0  | Port C               |

| 0  | 1  | 1  | Control register     |

| 1  | Х  | X  | 8255 is not selected |

The control register must be programmed to select the operation mode of the three ports A, B, and C.

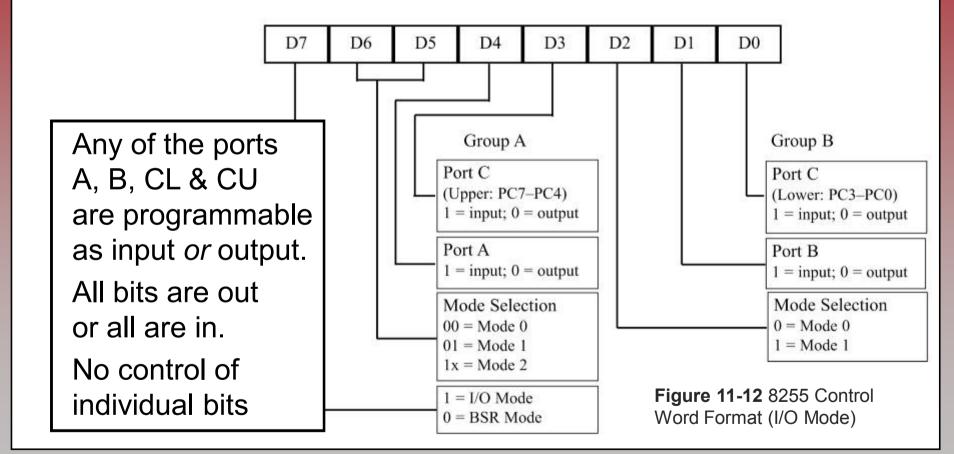

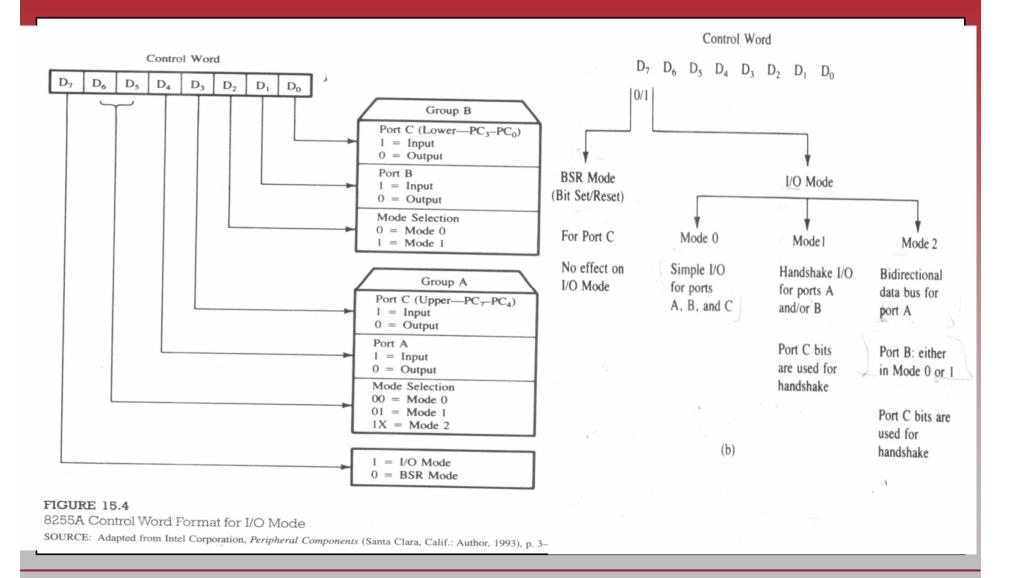

# 11.4: PROGRAMMING & INTERFACING THE 8255 mode selection of the 8255A

8255 ports can be programmed in various modes.

The *simple I/O mode*, Mode 0, is most widely used.

# 11.4: PROGRAMMING & INTERFACING THE 8255 mode selection of the 8255A

- In simple mode, any of the ports A, B, CL, and CU can be programmed as input or output.

- All bits are out or all are in.

- No control of individual bits

#### 8255 Control Word Format

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

#### Addressing an 8255

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

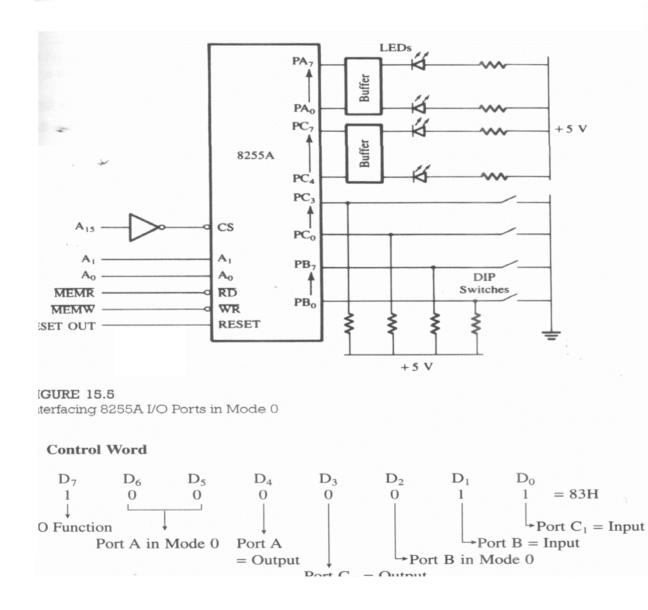

#### Mode 0 - Simple input/output

- Simple I/O mode: any of the ports A, B, CL, and CU can be programmed as input or output.

- Example: Configure port <u>A as input</u>, <u>B as output</u>, and all the bits of <u>port C as output</u> assuming a base address of 50h

- Control word should be 1001 0000b = 90h

PORTA EQU 50h PORTB EQU 51h PORTC EQU 52h CNTREG EQU 53h MOV AL, 90h OUT CNTREG,AL IN AL, PORTA OUT PORTB, AL OUT PORTC, AL

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

# Mod 0 Simple I/O

Initialize this device with the appropriate Control Word. Read from PORT  $C_L$  and display at PORT A.

PORT A 8000h PORT B 8001H PORT C 8002H CONTROL 8003H

Be careful Memory I/O! MOV AL,83H MOV BX,8003H MOV [BX],AL MOV BX,8002H MOV AL,[BX] AND AL,0FH DEC BX DEC BX MOV [BX],AL

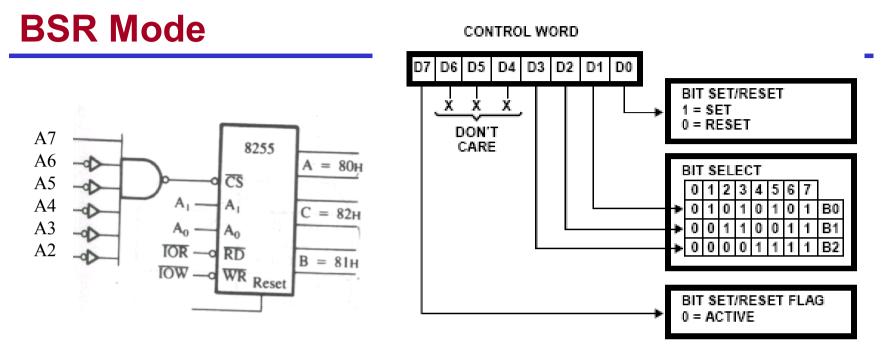

FIGURE 5. BIT SET/RESET FORMAT

>Concerned with the eight bits of port C only which can be set or reset by writing appropriate control word with D7=1

> It does not alter the previously transmitted control word with D7=0

| ≻Ex: Write a BSR word subroutine to set                     |  | MOV AL,0FH |

|-------------------------------------------------------------|--|------------|

| PC7 and PC3                                                 |  | OUT 83H,AL |

|                                                             |  | MOV AL,07H |

| To Set PC7 $\rightarrow$ OFH ; To set PC3 $\rightarrow$ 07H |  | OUT 83h,AL |

# **Example 11.4 of Textbook**

- Find the control word

- PA = out

- PB = in

- PC0 PC3 = in

- PC4 PC7 = out

- Program the 8255 to get data from port B and send it to port A; in addition data from PCL is sent out to the PCU

- Use port addresses 300h 303h for the 8255 chip

Control Word: The control word should be 1000 0011b = 83h

# Program

| B8255      | EQU    | 300h |  |  |

|------------|--------|------|--|--|

| CNTL       | EQU    | 83h  |  |  |

|            |        |      |  |  |

| MOV DX,B8  | 8255+3 |      |  |  |

| MOV AL,CN  | ITL    |      |  |  |

| OUT DX,AL  |        |      |  |  |

| MOV DX,B8  | 3255+1 |      |  |  |

| IN AL,DX   |        |      |  |  |

| MOV DX,B8  | 3255   |      |  |  |

| OUT DX,AL  |        |      |  |  |

| MOV DX,B8  | 3255+2 |      |  |  |

| IN AL,DX   |        |      |  |  |

| AND AL,0Fh | า      |      |  |  |

| MOV CL,4   |        |      |  |  |

| ROL AL,CL  |        |      |  |  |

| OUT DX,AL  |        |      |  |  |

|            |        |      |  |  |

# **Example 11-6 Textbook**

- Assume 8255 has a base address 300h

- Write a program to toggle all bits of port A continuously with a ¼ sec.

Delay

- Use int 16h to exit if there is a key press

|        | MOV DX,303h  |

|--------|--------------|

|        | MOV AL,80h   |

|        | OUT DX,AL    |

| AGAIN: | MOV DX,300h  |

|        | MOV AL,55h   |

|        | OUT DX,AL    |

|        | CALL QSDELAY |

|        | MOV AL,0AAh  |

|        | OUT DX,AL    |

|        |              |

# **Example Contd**

|         | CALL QSDELAY                                                                                      |

|---------|---------------------------------------------------------------------------------------------------|

|         | MOV AH,01                                                                                         |

|         | INT 16h                                                                                           |

|         | JZAGAIN                                                                                           |

|         | MOV AH,4Ch                                                                                        |

|         | INT 21h                                                                                           |

|         | sor independent delay IBM made PB4 of port 61h to toggle every c. (for 286 and higher processors) |

| QSDELAY | PROC NEAR                                                                                         |

|         | MOV CX,16572 ;16572*15.085 microsec = 1/4 s                                                       |

|         | PUSH AX                                                                                           |

| W1:     | IN AL,61h                                                                                         |

|         | AND AL,00010000b                                                                                  |

|         | CMP AL,AH                                                                                         |

|         | JE W1                                                                                             |

|         | MOV AH,AL                                                                                         |

|         | LOOP W1                                                                                           |

|         | POPAX                                                                                             |

|         | RET                                                                                               |

| QSDELAY | ENDP                                                                                              |

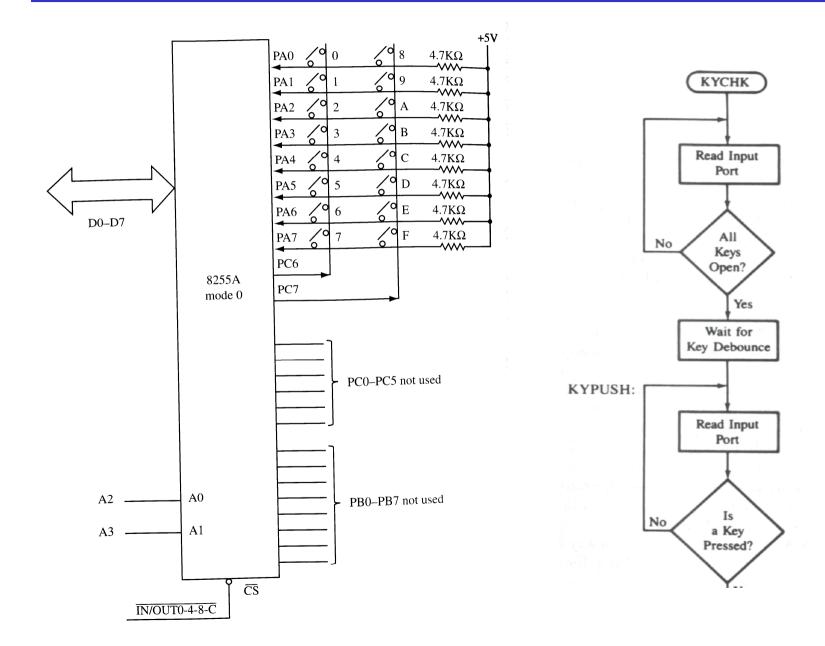

#### Mode 0 Design Example - Interfacing a matrix keyboard

64

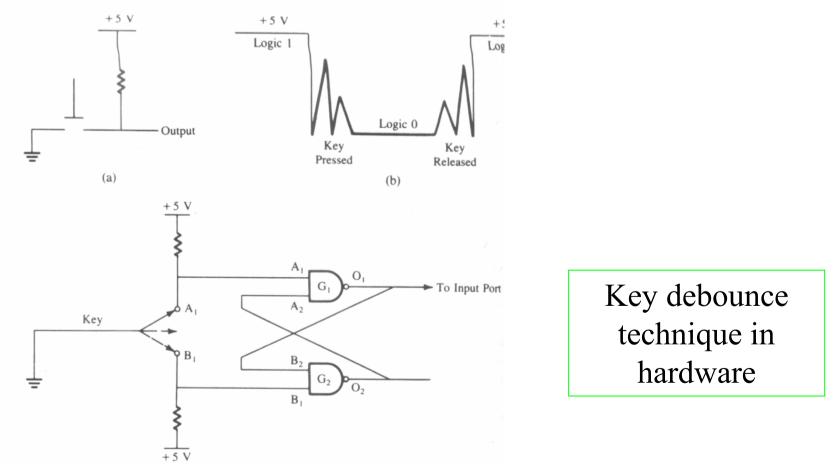

# **Key Debounce**

$\checkmark$  When a mechanical push button key is pressed or released the metal contacts of the key momentarily bounce before giving a steady-state reading. Therefore it is necessary that the bouncing of the key not be read as an input.

✓ Key debounce can be eliminated using either software or hardware.

|                                                             | ;Function:<br>;<br>;<br>;Inputs:<br>;Outputs:<br>;Calls:<br>;Destroys:     | and retu<br>value in<br>none<br>hex key | e keyboard shown in F<br>arn with the encoded<br>a register AL.<br>value in AL.<br>elay procedure for de<br>Elags | key                                                                                                                                                                                   |

|-------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                             | ;******<br>; Set up segm<br>;******                                        | ent to sto                              | ore key values                                                                                                    |                                                                                                                                                                                       |

| 0000<br>0000 00 01 02 03 04<br>0005 05 06 07                | KEY_CODE<br>COL1                                                           | SEGMENT<br>DB<br>DB                     | BYTE<br>0,1,2,3,4<br>5,6,7                                                                                        |                                                                                                                                                                                       |

| 0008 08 09 0A 0B 0C<br>000D 0D 0E 0F<br>0010                | COL2<br>KEY_CODE                                                           | DB<br>DB<br>ENDS                        | 8,9,0АН,0ВН,0СН<br>0DH,0ЕН,0FH                                                                                    |                                                                                                                                                                                       |

| 0000                                                        | CODE                                                                       | SEGMENT<br>ASSUME                       | BYTE<br>CS:CODE,DS:KEY_CODE                                                                                       |                                                                                                                                                                                       |

|                                                             | ;******<br>;Program equat<br>;******                                       | ces                                     |                                                                                                                   |                                                                                                                                                                                       |

| <pre>= 00F0 = 00F2 = 00BF = 007F = 003F = 00FF = 16FA</pre> | PORT_A<br>PORT_C<br>COL_1_LOW<br>COL_2_LOW<br>BOTH_COL_LOW<br>KEY_UP<br>T1 | EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU  | 00H<br>08H<br>10111111B<br>0111111B<br>00111111B<br>0FFH<br>8B82H                                                 | ;PPI port A address (see Fig. 8.12)<br>;PPI port C address<br>;PC6 low<br>;PC7 low<br>;PC6 and PC7 low<br>;Input 0FFH when no keys are down<br>;~ 10 ms time delay assuming 25 MHz 80 |

; \* \* \* \* \* \* \* 10 ms time delay for debouncing \*\*\*\*\*\* NEAR PROC DELAY CX,T1 MOV COUNT LOOP COUNT: RET ENDP DELAY \*\*\*\*\*\* ; Main program begins here ; \* \* \* \* \* \* \* NEAR PROC KEYBOARD ;Save registers about to be used DS PUSH PUSH СХ PUSH SI ; Point DS to the key codes AX, KEY\_CODE MOV DS,AX MOV ;Wait for previous key to be released ;Scan both columns AL, BOTH\_COL\_LOW MOV ;Column lines on PC6 and PC7 PORT\_C,AL OUT ;Read keyboard AL, PORT\_A IN POLL1: ;All keys up? AL, KEY\_UP CMP ;No - so wait POLL1 JNE ;Yes - wait for bounce on release DELAY CALL ;Wait for a new key to be pressed ;Read keyboard AL, PORT\_A POLL2: IN ;Any keys down? AL, KEY\_UP CMP ;No - so wait POLL2 JΕ ;Yes - wait for bounce DELAY CALL

|      |              | ;See if the key | v is in ( | column 1              |                                       |

|------|--------------|-----------------|-----------|-----------------------|---------------------------------------|

| 0024 | B0 BF        |                 | MOV       | AL,COL_1_LOW          | ;Test for column 1                    |

| 0026 | E6 08        |                 | OUT       | PORT_C,AL             | ; PC6 low                             |

| 0028 | E4 00        |                 | IN        | AL, PORT_A            | ;Read column 1 keys                   |

| 002A | 3C FF        |                 | CMP       | AL, KEY_UP            | ;Any key down?                        |

| 002C | 74 07        |                 | JE        | CHECK_COL_2           | ;No - check for column 2              |

| 002E | 8D 36 0000 R |                 | LEA       | SI,COL1               | ;Yes - point SI at the key values 0-7 |

| 0032 | EB 0F 90     |                 | JMP       | LOOKUP                | ;Now lookup code                      |

|      |              |                 | 0111      |                       | ,NOW TOOKUP CODE                      |

|      |              | If not column 1 | then co   | olumn 2               |                                       |

| 0035 | B0 7F        | CHECK_COL_2:    | MOV       | AL,COL_2_LOW          | ;Test for column 2                    |

| 0037 | E6 08        |                 | OUT       | PORT_C,AL             | ;PC7 low                              |

| 0039 | E4 00        |                 | IN        | AL, PORT_A            | ;Read column 2 keys                   |

| 003B | 3C FF        |                 | CMP       | AL,KEY_UP             | ;Any key down?                        |

| 003D | 74 DC        |                 | JE        | POLL2                 | ;No - false input so repeat           |

| 003F | 8D 36 0008 R |                 | LEA       | SI,COL2               | ;Yes - point SI at key values 8-F     |

|      |              | ;Now lookup the | e key's v | value and store in AL |                                       |

| 0043 | D0 D8        | LOOKUP:         | RCR       | AL,1                  | ;Rotate keyboard input code right     |

| 0045 | 73 03        |                 | JNC       | МАТСН                 | ; If 0 key is found - so retrieve it  |

| 0047 | 46           |                 | INC       | SI                    | ;No - advance pointer to next value   |

| 0048 | EB F9        |                 | JMP       | LOOKUP                | ;Repeat the loop                      |

|      |              |                 |           |                       |                                       |

| 004A | 8A 04        | MATCH:          | MOV       | AL,[SI]               | ;Get the key code                     |

| 004C | 5E           |                 | POP       | SI                    | Restore all registers                 |

| 004D | 59           |                 | POP       | СХ                    | ;(except AX and flags)                |

| 004E | 1F           |                 | POP       | DS                    |                                       |

| 004F | C3           |                 | RET       |                       |                                       |

| 0050 |              | KEYBOARD        | ENDP      |                       |                                       |

| 0050 |              | CODE            | ENDS      |                       |                                       |

|      |              |                 | END       | KEYBOARD              |                                       |

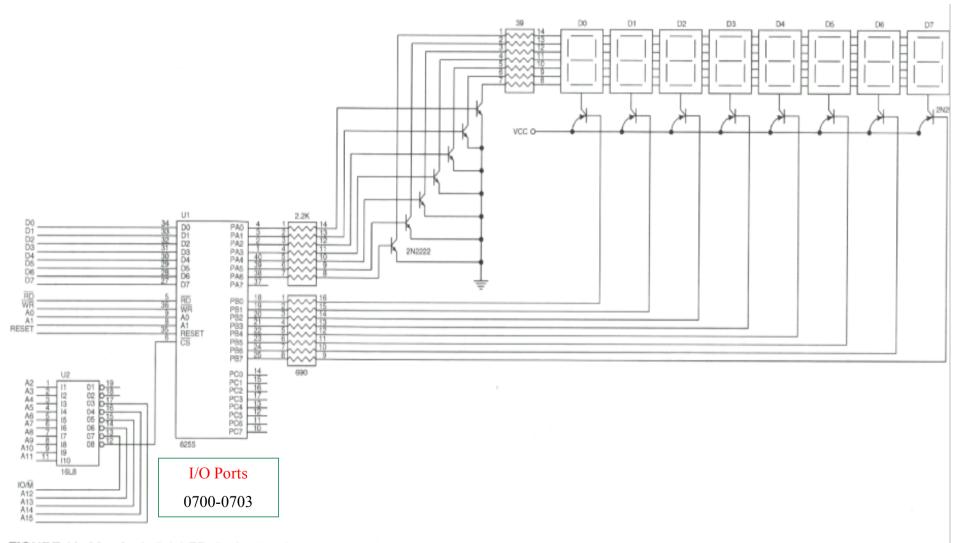

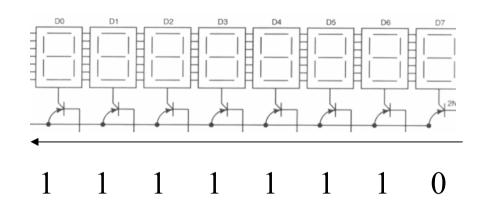

# 8 Digit LED

FIGURE 11-20 An 8-digit LED display interfaced to the 8088 microprocessor through an 82C55 PIA.

# 8 Digit LED

; INIT 8255 MOV AL,10000000B MOV DX,703H OUT DX,AL

;SETUP REGISTERS TO DISPLAY MOV BX,7 MOV AH,7FH MOV SI,OFFSET MEM MOV DX.701H

; DISPLAY 8 DIGITS

DISP1: MOV AL,AH ;select digit OUT DX,AL DEC DX ;address PORT A MOV AL,[BX+SI] OUT DX,AL CALL DELAY ;wait 1 ms ROR AH,1 INC DX ;address PORT B DEC BX ;adjust count JNZ DISP1

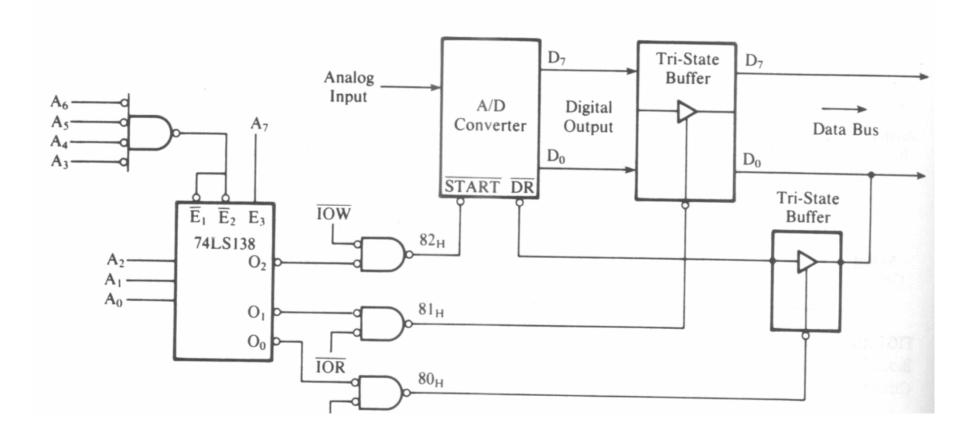

### Using A/D with status check (polling)

# **Connecting the 804 A/D**

| PA0-PA7 to DO-D7 of ADC | CHANNEL SELECTION(out), DATA READ (in) |  |  |

|-------------------------|----------------------------------------|--|--|

| PB0 TO INTR             | PORT B AS INPUT                        |  |  |

| PC0 TO WR               | PORT C AS OUTPUT                       |  |  |

| PC1 TO RD               | PORT C AS OUTPUT                       |  |  |

# **Required Steps**

- CS=0 WR=0

- Provide the address of the selected channel on DB0 DB7

- Apply a WR pulse

- Channel 2 address is 09h, Channel 1 address is 08h, etc.

- Not only we select the channel but conversion starts!

- While WR=1

- Keep monitoring INTR asserted low

- When INTR goes low, conversion finished

- After INTR becomes low

- CS=0 and WR=1 and apply a low pulse to the RD pin to get the data from the 848 IC chip

# **Example**

```

MOV AL,82h ;PA=out PB=in PC=out

MOV DX, CNT PORT

OUT DX,AL

MOV AL,09 ;channel 2 address

MOV DX, PORT A

OUT DX,AL

MOV AL,02 ;WR=0 RD=1

MOV DX, PORT C ; not only selects channel but also

; starts conversion

OUT DX,AL

CALL DELAY ;few microsecs

MOV AL,03 ; WR=1 RD=1

OUT DX,AL

CALL DELAY

MOV AL,92h ; PA=in PB=in PC=out

MOV DX, CNT_PORT

OUT DX,AL

```

# Example

MOV DX,PORT\_B B1: IN AL,DX AND AL,01 CMP AL,01 JNE B1 MOV AL,01 ;RD=0 MOV DX,PORT\_C OUT DX,AL MOV DX,PORT\_A IN AL,DX ;get the converted data

# The x86 PC

assembly language, design, and interfacing fifth edition

MUHAMMAD ALI MAZIDI JANICE GILLISPIE MAZIDI DANNY CAUSEY